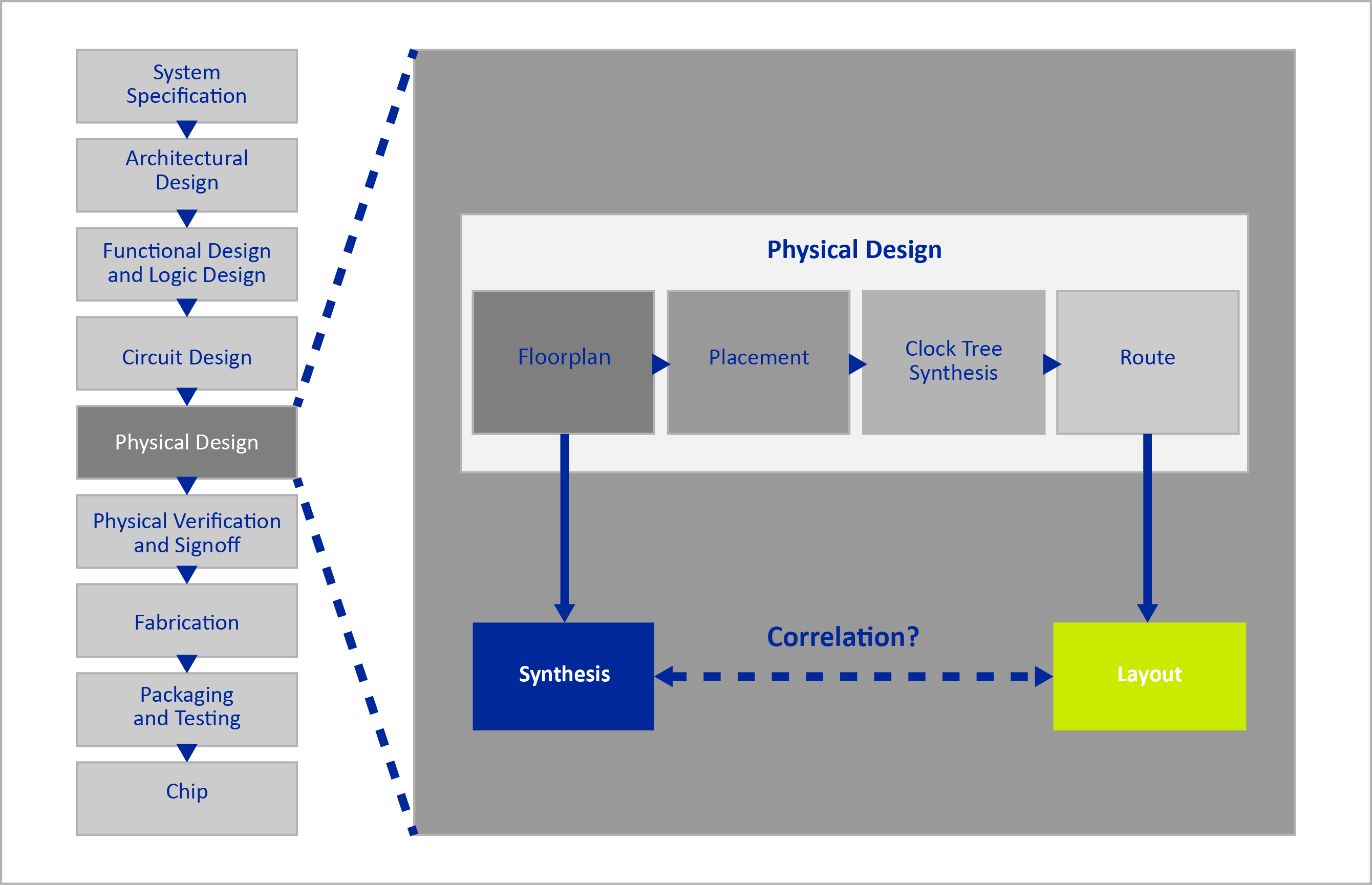

In theory, physical synthesis tools have all the necessary information about the layout; in practice, they must be correlated very carefully to real-world layout data.

The design of a chip involves many stages, from system specification and architectural design, all the way to the fabrication and packaging of the final silicon that goes into a device. During this cycle, it is crucial to have reliable estimates of timing and area in order to plan properly and meet expectations.

Read the full article published on EETimes.

The Article will take a look into the physical design (or backend design) portion of the process; specifically, at the correlation of timing and area within the steps associated with the physical design.

You might also like

More from Deep Learning

How The Smart Edge Drives Demand For Efficient Chip Design Strategies

Iri Trashanski, Chief Strategy Officer at Ceva, is shaping the future of the Smart Edge with extensive experience across tech sectors. Back …

Hearables Featuring AI are Gaining Traction

Our demand for ever higher quality audio devices continues to drive innovation. Mobility through hearables (earbuds, wireless headphones and gaming …

The AIPC is Reinventing PC Hardware

We first started hearing about AI-enabled PCs (AIPCs) from Microsoft. As a platform, PCs may seem a mature and unpromising …